Data61 Trustworthy Systems https://ts.data61.csiro.au/projects/TS/

# seL4 MCS Reference Manual Version 9.0.0-MCS

Trustworthy Systems Team, Data61 https://sel4.systems/contact/

12 April 2018

C 2018 General Dynamics C4 Systems.

All rights reserved.

#### Acknowledgements

The primary authors of this document are Matthew Grosvenor and Adam Walker, with contributions from Adrian Danis, Andrew Boyton, David Greenaway, Etienne Le Sueur, Gernot Heiser, Gerwin Klein, Godfrey van der Linden, Kevin Elphinstone, Matthew Fernandez, Matthias Daum, Michael von Tessin, Peter Chubb, Simon Winwood, Thomas Sewell, Timothy Bourke and Toby Murray. All authors and contributors can be contacted at firstname.lastname@data61.csiro.au.

# Contents

| 1        | Intr | oducti  | on                                    | 1        |

|----------|------|---------|---------------------------------------|----------|

| <b>2</b> | Ker  | nel Sei | rvices and Objects                    | <b>2</b> |

|          | 2.1  | Capab   | ility-based Access Control            | 2        |

|          | 2.2  | System  | n Calls                               | 3        |

|          | 2.3  | Kernel  | Objects                               | 5        |

|          | 2.4  | Kernel  | Memory Allocation                     | 6        |

|          |      | 2.4.1   | Reusing Memory                        | 7        |

|          |      | 2.4.2   | Summary of Object Sizes               | 8        |

| 3        | Cap  | ability | Spaces                                | 9        |

|          | 3.1  | Capab   | ility and CSpace Management           | 10       |

|          |      | 3.1.1   | CSpace Creation                       | 10       |

|          |      | 3.1.2   | CNode Methods                         | 10       |

|          |      | 3.1.3   | Capabilities to Newly-Retyped Objects | 11       |

|          |      | 3.1.4   | Capability Rights                     | 11       |

|          |      | 3.1.5   | Capability Derivation Tree            | 11       |

|          | 3.2  | Deletic | on and Revocation                     | 13       |

|          | 3.3  | CSpace  | e Addressing                          | 13       |

|          |      | 3.3.1   | Capability Address Lookup             | 14       |

|          |      | 3.3.2   | Addressing Capabilities               | 15       |

|          | 3.4  | Looku   | p Failure Description                 | 17       |

|          |      | 3.4.1   | Invalid Root                          | 17       |

|          |      | 3.4.2   | Missing Capability                    | 17       |

|          |      | 3.4.3   | Depth Mismatch                        | 17       |

|          |      | 3.4.4   | Guard Mismatch                        | 18       |

| <b>4</b> | Mes    | ssage F | Passing (IPC)                                                                                             | 19        |

|----------|--------|---------|-----------------------------------------------------------------------------------------------------------|-----------|

|          | 4.1    | Messag  | ge Registers                                                                                              | 19        |

|          | 4.2    | Endpo   | ints                                                                                                      | 20        |

|          |        | 4.2.1   | Endpoint Badges                                                                                           | 20        |

|          |        | 4.2.2   | Capability Transfer                                                                                       | 21        |

|          |        | 4.2.3   | Errors                                                                                                    | 21        |

| -        | NT - 4 | :e      |                                                                                                           | 0.0       |

| 5        |        |         |                                                                                                           | 23        |

|          | 5.1    |         | eation Objects                                                                                            |           |

|          | 5.2    | _       | ling, Polling and Waiting                                                                                 |           |

|          | 5.3    | Bindin  | g Notifications                                                                                           | 24        |

| 6        | Thr    | eads a  | nd Scheduling contexts                                                                                    | <b>25</b> |

|          | 6.1    | Thread  | ls                                                                                                        | 25        |

|          |        | 6.1.1   | Thread control blocks                                                                                     | 25        |

|          |        | 6.1.2   | Thread Creation $\ldots$ | 25        |

|          |        | 6.1.3   | Thread Deactivation $\ldots \ldots \ldots$ | 26        |

|          |        | 6.1.4   | Scheduling Contexts                                                                                       | 26        |

|          |        | 6.1.5   | Passive Threads                                                                                           | 27        |

|          |        | 6.1.6   | Scheduling Context Creation                                                                               | 28        |

|          |        | 6.1.7   | Scheduling Context Donation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                     | 28        |

|          |        | 6.1.8   | Scheduling algorithm                                                                                      | 29        |

|          |        | 6.1.9   | Exceptions                                                                                                | 30        |

|          |        |         | 6.1.9.1 Standard Exceptions                                                                               | 30        |

|          |        |         | 6.1.9.2 Timeout Exceptions $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                      | 30        |

|          |        | 6.1.10  | Message Layout of the Read-/Write-Registers Methods                                                       | 31        |

|          | 6.2    | Faults  |                                                                                                           | 31        |

|          |        | 6.2.1   | Capability Faults                                                                                         | 31        |

|          |        | 6.2.2   | Unknown Syscall                                                                                           | 32        |

|          |        | 6.2.3   | User Exception $\ldots$  | 32        |

|          |        | 6.2.4   | Debug Exception: Breakpoints and Watchpoints $\ . \ . \ . \ .$                                            | 32        |

|          |        | 6.2.5   | Debug Exception: Single-stepping                                                                          | 33        |

|          |        | 6.2.6   | Timeout Fault                                                                                             | 34        |

|          |        | 6.2.7   | VM Fault                                                                                                  | 35        |

|    | 6.3  | Domains                                                                                                                                           | 35        |

|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|    | 6.4  | Virtualisation                                                                                                                                    | 36        |

|    |      | 6.4.1 ARM                                                                                                                                         | 36        |

|    |      | $6.4.2  x86 \ldots \ldots$ | 36        |

| 7  | Add  | lress Spaces and Virtual Memory                                                                                                                   | 38        |

| •  | 7.1  | Overview                                                                                                                                          |           |

|    | 1.1  | 7.1.0.0.1 IA-32                                                                                                                                   |           |

|    |      | 7.1.0.0.2 ARM                                                                                                                                     | 38        |

|    | 7.2  | Objects                                                                                                                                           |           |

|    | 1.2  | 7.2.0.0.1 Page Directory                                                                                                                          |           |

|    |      | 7.2.0.0.2 Page Table                                                                                                                              |           |

|    |      | 7.2.0.0.3 Page                                                                                                                                    | 40        |

|    |      | 7.2.0.0.4 ASID Control                                                                                                                            |           |

|    |      | 7.2.0.0.5 ASID Pool                                                                                                                               |           |

|    | 7.3  | Mapping Attributes                                                                                                                                |           |

|    | 7.4  | Sharing Memory                                                                                                                                    |           |

|    | 7.5  | Page Faults                                                                                                                                       |           |

|    |      |                                                                                                                                                   |           |

| 8  | Har  | dware I/O                                                                                                                                         | 42        |

|    | 8.1  | Interrupt Delivery                                                                                                                                | 42        |

|    | 8.2  | x86-Specific I/O                                                                                                                                  | 42        |

|    |      | 8.2.1 Interrupts                                                                                                                                  | 42        |

|    |      | 8.2.2 I/O Ports                                                                                                                                   | 43        |

|    |      | 8.2.3 I/O Space                                                                                                                                   | 43        |

| 9  | Syst | tem Bootstrapping                                                                                                                                 | 45        |

|    | 9.1  | Initial Thread's Environment                                                                                                                      | 45        |

|    | 9.2  | BootInfo Frame                                                                                                                                    | 45        |

|    | 9.3  | Boot Command-line Arguments                                                                                                                       | 48        |

| 10 | T    | 4 API Reference                                                                                                                                   | 40        |

| 10 |      | Error Codes                                                                                                                                       | <b>49</b> |

|    | 10.1 | 10.1.1 Invalid Argument                                                                                                                           | 49        |

|    |      |                                                                                                                                                   | 49        |

|    |      | 10.1.2 Invalid Capability                                                                                                                         | 49        |

| 10.1.3      | Illegal Operation                                                                    | 49 |

|-------------|--------------------------------------------------------------------------------------|----|

| 10.1.4      | Range Error                                                                          | 50 |

| 10.1.5      | Alignment Error                                                                      | 50 |

| 10.1.6      | Failed Lookup                                                                        | 50 |

| 10.1.7      | Delete First                                                                         | 50 |

| 10.1.8      | Revoke First                                                                         | 50 |

| 10.1.9      | Not Enough Memory                                                                    | 51 |

| 10.2 System | Calls                                                                                | 51 |

| 10.2.1      | General System Calls                                                                 | 51 |

|             | 10.2.1.1 Send                                                                        | 51 |

|             | 10.2.1.2 Recv                                                                        | 51 |

|             | 10.2.1.3 Call                                                                        | 52 |

| -<br>-      | 10.2.1.4 Polling Send                                                                | 52 |

|             | 10.2.1.5 Polling Recv $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 53 |

| -           | 10.2.1.6 Reply Recv                                                                  | 53 |

| -           | 10.2.1.7 NBSend Recv                                                                 | 54 |

| -           | 10.2.1.8 NBSend Wait                                                                 | 54 |

|             | 10.2.1.9 Yield                                                                       | 55 |

| -           | 10.2.1.10 Wait                                                                       | 55 |

| -           | 10.2.1.11 NBWait                                                                     | 56 |

|             | 10.2.1.12 Poll                                                                       | 56 |

|             | 10.2.1.13 Signal                                                                     | 57 |

| 10.2.2      | Debugging System Calls                                                               | 58 |

|             | 10.2.2.1 Put Char                                                                    | 58 |

|             | 10.2.2.2 Dump scheduler $\ldots$                                                     | 58 |

|             | 10.2.2.3 Halt                                                                        | 59 |

|             | 10.2.2.4 Snapshot $\ldots$                                                           | 59 |

|             | 10.2.2.5 Cap Identify $\ldots$                                                       | 59 |

|             | 10.2.2.6 Name Thread                                                                 | 60 |

|             | 10.2.2.7 Run                                                                         | 60 |

| 10.2.3      | Benchmarking System Calls                                                            | 61 |

|             | 10.2.3.1 Reset Log                                                                   | 61 |

|             | 10.2.3.2 Finalize Log                                                                | 62 |

|      | 10.3.26 | OTCB - Set Sched Params    8                                      | 6 |

|------|---------|-------------------------------------------------------------------|---|

|      | 10.3.27 | TCB - Set Space                                                   | 7 |

|      | 10.3.28 | BTCB - Set Timeout Endpoint                                       | 7 |

|      | 10.3.29 | TCB - Suspend                                                     | 8 |

|      | 10.3.30 | TCB - Unbind Notification                                         | 8 |

|      | 10.3.31 | TCB - Unset Breakpoint                                            | 9 |

|      | 10.3.32 | 2 TCB - Write Registers                                           | 9 |

|      | 10.3.33 | Untyped - Retype                                                  | 0 |

|      | 10.3.34 | lseL4_SchedContext - Bind                                         | 1 |

|      | 10.3.35 | SeL4_SchedContext - Consumed                                      | 1 |

|      | 10.3.36 | $seL4\_SchedContext - Unbind \dots 92$                            | 2 |

|      | 10.3.37 | $seL4\_SchedContext - UnbindObject \dots 92$                      | 2 |

|      | 10.3.38 | SeL4_SchedContext - YieldTo                                       | 3 |

|      | 10.3.39 | eseL4_SchedControl - Configure                                    | 4 |

| 10.4 | x86-Sp  | ecific Object Methods                                             | 5 |

|      | 10.4.1  | General x86 Object Methods                                        | 5 |

|      |         | 10.4.1.1 ASID Control - Make Pool                                 | 5 |

|      |         | 10.4.1.2 ASID Pool - Assign                                       | 6 |

|      |         | 10.4.1.3 Extended Page Table Page Directory - Map 9               | 6 |

|      |         | 10.4.1.4 Extended Page Table Page Directory - Unmap 9             | 7 |

|      |         | 10.4.1.5 Extended Page Table Page Directory Page Table - Map 9    | 7 |

|      |         | 10.4.1.6 Extended Page Table Page Directory Page Table - Unmap 99 | 8 |

|      |         | 10.4.1.7 Extended Page Table Page Table - Map 9                   | 8 |

|      |         | 10.4.1.8 Extended Page Table Page Table - Unmap 99                | 9 |

|      |         | 10.4.1.9 I/O Page Table - Map                                     | 9 |

|      |         | 10.4.1.10 I/O Page Table - Unmap                                  | 0 |

|      |         | 10.4.1.11 I/O Port - In16                                         | 0 |

|      |         | 10.4.1.12 I/O Port - In32                                         | 0 |

|      |         | 10.4.1.13 I/O Port - In8                                          | 1 |

|      |         | 10.4.1.14 I/O Port - Out16                                        | 1 |

|      |         | 10.4.1.15 I/O Port - Out32                                        | 2 |

|      |         | 10.4.1.16 I/O Port - Out8                                         |   |

|      |         | 10.4.1.17 IRQ Control - Get I/O APIC                              | 3 |

10.5

| 1 |

|---|

|   |

| 5 |

| 5 |

| 3 |

| 3 |

| 7 |

| 7 |

| 3 |

| 3 |

| ) |

| ) |

| ) |

| ) |

| L |

| L |

| 2 |

| 2 |

| 3 |

| 1 |

| 5 |

| 5 |

| 5 |

| 3 |

| 3 |

| 3 |

| 7 |

| 7 |

| 3 |

| 3 |

| ) |

| ) |

| ) |

|   |

|        | 10.5.1.9 Page - Map I/O                                                                    |

|--------|--------------------------------------------------------------------------------------------|

|        | 10.5.1.10 Page - Map                                                                       |

|        | 10.5.1.11 Page - Remap                                                                     |

|        | 10.5.1.12 Page - Unify Instruction                                                         |

|        | 10.5.1.13 Page - Unmap                                                                     |

|        | 10.5.1.14 Page Table - Map                                                                 |

|        | 10.5.1.15 Page Table - Unmap                                                               |

|        | 10.5.1.16 VCPU - Inject IRQ                                                                |

|        | 10.5.1.17 VCPU - Read Registers                                                            |

|        | 10.5.1.18 VCPU - Set TCB                                                                   |

|        | 10.5.1.19 VCPU - Write Registers                                                           |

| 10.5.2 | Aarch32-Specific Object Methods                                                            |

|        | 10.5.2.1 Page Directory - Clean Data                                                       |

|        | 10.5.2.2 Page Directory - Clean and Invalidate Data 126                                    |

|        | 10.5.2.3 Page Directory - Invalidate Data                                                  |

|        | 10.5.2.4 Page Directory - Unify Instruction                                                |

| 10.5.3 | Aarch64-Specific Object Methods                                                            |

|        | 10.5.3.1 Page Directory - Map                                                              |

|        | 10.5.3.2 Page Directory - Unmap                                                            |

|        | 10.5.3.3 Page Global Directory - Clean Data                                                |

|        | 10.5.3.4 Page Global Directory - Clean and Invalidate Data $~$ . 129                       |

|        | 10.5.3.5 Page Global Directory - Invalidate Data                                           |

|        | 10.5.3.6 Page Global Directory - Unify Instruction                                         |

|        | 10.5.3.7 Page Upper Directory - Map $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 131$ |

|        | 10.5.3.8 Page Upper Directory - Unmap                                                      |

# List of Tables

| 3.1 | seL4 access rights.                                                                                                        | 11 |

|-----|----------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Capability derivation.                                                                                                     | 12 |

| 4.1 | Fields of the seL4_IPCBuffer structure. Note that badges and caps use the same area of memory in the structure             | 20 |

| 6.1 | Contents of an IPC message.                                                                                                | 32 |

| 6.2 | Debug fault message layout. The register API-ID is not returned in the fault message from the kernel on single-step faults | 34 |

| 6.3 | Single-step fault message layout.                                                                                          | 34 |

| 6.4 | Timeout fault outcome on 32-bit architectures                                                                              | 35 |

| 6.5 | VM Fault outcome on all architectures.                                                                                     | 35 |

| 7.1 | Virtual memory attributes for ARM page table entries.                                                                      | 41 |

| 7.2 | Virtual memory attributes for x86 page table entries                                                                       | 41 |

| 9.1 | Initial thread's CNode content.                                                                                            | 46 |

| 9.2 | BootInfo struct                                                                                                            | 47 |

| 9.3 | BootInfoHeader struct                                                                                                      | 48 |

| 9.4 | seL4_UntypedDesc struct $\ldots \ldots \ldots$              | 48 |

| 9.5 | IA-32 boot command-line arguments                                                                                          | 48 |

# List of Figures

| 3.1 | Example capability derivation tree                                       | 12 |

|-----|--------------------------------------------------------------------------|----|

| 3.2 | An example CSpace demonstrating object references at all levels, various |    |

|     | guard and radix sizes and internal CNode references                      | 15 |

| 3.3 | An arbitrary CSpace layout                                               | 16 |

## Chapter 1

## Introduction

The seL4 microkernel is an operating-system kernel designed to be a secure, safe, and reliable foundation for systems in a wide variety of application domains. As a microkernel, it provides a small number of services to applications, such as abstractions to create and manage virtual address spaces, threads, and inter-process communication (IPC). The small number of services provided by seL4 directly translates to a small implementation of approximately 8700 lines of C code. This has allowed the ARMv6 version of the kernel to be formally proven in the Isabelle/HOL theorem prover to adhere to its formal specification [Boy09, CKS08, DEK<sup>+</sup>06, EKE08, KEH<sup>+</sup>09, TKN07, WKS<sup>+</sup>09], which in turn enabled proofs of the kernel's enforcement of integrity [SWG<sup>+</sup>11] and confidentiality [MMB<sup>+</sup>13]. The kernel's small size was also instrumental in performing a complete and sound analysis of worst-case execution time [BSC<sup>+</sup>11, BSH12].

This manual describes the seL4 kernel's API from a user's point of view. The document starts by giving a brief overview of the seL4 microkernel design, followed by a reference of the high-level API exposed by the seL4 kernel to userspace.

While we have tried to ensure that this manual accurately reflects the behaviour of the seL4 kernel, this document is by no means a formal specification of the kernel. When the precise behaviour of the kernel under a particular circumstance needs to be known, users should refer to the seL4 abstract specification, which gives a formal description of the seL4 kernel.

## Chapter 2

## Kernel Services and Objects

A limited number of service primitives are provided by the microkernel; more complex services may be implemented as applications on top of these primitives. In this way, the functionality of the system can be extended without increasing the code and complexity in privileged mode, while still supporting a potentially wide number of services for varied application domains.

The basic services seL4 provides are as follows:

Threads are an abstraction of CPU execution that supports running software;

- Scheduling contexts are an abstraction of CPU execuion time.

- Address spaces are virtual memory spaces that each contain an application. Applications are limited to accessing memory in their address space;

- **Inter-process communication** (IPC) via *endpoints* allows threads to communicate using message passing;

- **Reply objects** are used to store single-use reply capabilities, and are provided by the receiver during message passing.

- Notifications provide a non-blocking signalling mechanism similar to binary semaphores;

- **Device primitives** allow device drivers to be implemented as unprivileged applications. The kernel exports hardware device interrupts via IPC messages; and

- **Capability spaces** store capabilities (i.e., access rights) to kernel services along with their book-keeping information.

This chapter gives an overview of these services, describes how kernel objects are accessed by userspace applications, and describes how new objects can be created.

## 2.1 Capability-based Access Control

The seL4 microkernel provides a capability-based access-control model. Access control governs all kernel services; in order to perform an operation, an application must *invoke*

a capability in its possession that has sufficient access rights for the requested service. With this, the system can be configured to isolate software components from each other, and also to enable authorised, controlled communication between components by selectively granting specific communication capabilities. This enables software-component isolation with a high degree of assurance, as only those operations explicitly authorised by capability possession are permitted.

A capability is an unforgeable token that references a specific kernel object (such as a thread control block) and carries access rights that control what methods may be invoked. Conceptually, a capability resides in an application's *capability space*; an address in this space refers to a *slot* which may or may not contain a capability. An application may refer to a capability—to request a kernel service, for example—using the address of the slot holding that capability. This means, the seL4 capability model is an instance of a *segregated* (or *partitioned*) capability system, where capabilities are managed by the kernel.

Capability spaces are implemented as a directed graph of kernel-managed *capability nodes* (CNodes). A CNode is a table of slots, where each slot may contain further CNode capabilities. An address of a capability in a capability space is the concatenation of the indices of slots within CNodes forming the path to the destination slot; we discuss CNode objects in detail in Chapter 3.

Capabilities can be copied and moved within capability spaces, and also sent via IPC. This allows creation of applications with specific access rights, the delegation of authority to another application, and passing to an application authority to a newly created (or selected) kernel service. Furthermore, capabilities can be *minted* to create a derived capability with a subset of the rights of the original capability (never with more rights). A newly minted capability can be used for partial delegation of authority.

Capabilities can also be revoked to withdraw authority. Revocation recursively removes any capabilities that have been derived from the original capability being revoked. The propagation of capabilities through the system is controlled by a *take-grant*-based model [EKE08, Boy09].

### 2.2 System Calls

The seL4 kernel provides a message-passing service for communication between threads. This mechanism is also used for communication with kernel-provided services. There is a standard message format, each message containing a number of data words and possibly some capabilities. The structure and encoding of these messages are described in detail in Chapter 4.

Threads send messages by invoking capabilities within their capability space. When an endpoint capability is invoked in this way, the message will be transferred through the kernel to another thread. When capabilities to kernel objects are invoked, the message will be interpreted as a method invocation in a manner specific to the type of kernel object. For example, invoking a thread control block (TCB) capability with a correctly formatted message will suspend the target thread.

Logically, the kernel provides three system calls, Send, Receive and Yield. However,

there are also combinations and variants of the basic *Send* and *Receive* calls, e.g. the *Call* operation, which consists of a send followed by a *Receive* from the same object. Methods on kernel objects other than endpoints and notifications are all mapped to *Send* or *Call*, depending on whether or not the method returns a result. The *Yield* system call is not associated with any kernel object and is the only operation that does not invoke a capability. *Wait* is a variant of *Receive* that does not require a reply object to be provided.

The complete set of system calls is:

- seL4\_Send() delivers a message through the named capability and the application to continue. If the invoked capability is an endpoint, and no receiver is ready to receive the message immediately, the sending thread will block until the message can be delivered. No error code or response will be returned by the receiving object.

- seL4\_NBSend() performs a polling send on an endpoint. It is similar to seL4\_Send(), except that it is guaranteed not to block. If the message cannot be delivered immediately, i.e. there is no receiver waiting on the destination Endpoint, the message is silently dropped. Like seL4\_Send(), no error code or response will be returned.

- seL4\_Wait() is used by a thread to receive messages through endpoints or notifications. If no sender or notification is pending, the caller will block until a message or notification can be delivered. This system call works only on Endpoint or Notification capabilities, raising a fault (see section 6.2) when attempted with other capability types.

- seL4\_NBWait() is used by a thread to poll for messages through endpoints or notifications. If no sender or notification is pending, the system call returns immediately.

- seL4\_Call() combines seL4\_Send() and seL4\_Recv(). The call blocks the sending thread until its message is delivered and a reply message is received. When the sent message is delivered to another thread (via an Endpoint), the kernel adds an additional 'reply' capability to the message that is delivered giving the receiver the right to reply to the original sender. The reply capability is deposited in a dedicated reply object provided by the receiver, and is a single-use right, meaning that the kernel invalidates it as soon as it has been invoked.

The seL4\_Call() operation exists not only for efficiency reasons (combining two operations into a single system call). It differs from seL4\_Send() immediately followed by seL4\_Recv() in two ways:

- 1. the single-use reply capability is created to establish a reply channel with minimal trust;

- 2. the transition from send to recv phase is atomic, meaning it cannot be preempted, and the receiver can reply without any risk of blocking.

When invoking capabilities to kernel services, using **seL4\_Call()** allows the kernel to return an error code or other response through the reply message.

- seL4\_ReplyRecv() combines an invocation of the reply capability (seL4\_Send()) and uses the same reply object for the seL4\_Recv() phase. It exists mostly for efficiency reasons: the common case of replying to a request and waiting for the next can be performed in a single kernel system call instead of two. The transition from the reply to the receive phase is also atomic.

- seL4\_NBRecv() is used by a thread to check for signals pending on a notification object or messages pending on an endpoint without blocking. This system call works only on endpoints and notification object capabilities, raising a fault (see section 6.2) when attempted with other capability types.

- seL4\_NBSendWait() combined an seL4\_NBSend() and seL4\_Wait() into one atomic system call.

- seL4\_NBSendRecv() combined an seL4\_NBSend() and seL4\_Recv() into one atomic system call.

- seL4\_Yield() is the only system call that does not require a capability to be used. It forfeits the remainder of the calling thread's timeslice and causes invocation of the kernel's scheduler. If there are no other runnable threads with the same priority as the caller, the calling thread will immediately be scheduled with a fresh timeslice, unless it is a sporadically scheduled thread, which will be scheduled when the next replenishment is due, see Section 6.1.4.

## 2.3 Kernel Objects

In this section we give a brief overview of the kernel-implemented object types whose instances (also simply called *objects*) can be invoked by applications. The interface to these objects forms the interface to the kernel itself. The creation and use of kernel services is achieved by the creation, manipulation, and combination of these kernel objects:

- **CNodes** (see Chapter 3) store capabilities, giving threads permission to invoke methods on particular objects. Each CNode has a fixed number of slots, always a power of two, determined when the CNode is created. Slots can be empty or contain a capability.

- **Thread Control Blocks** (TCBs; see Chapter 6) represent a thread of execution in seL4. Threads are the unit of execution that is scheduled, blocked, unblocked, etc., depending on the application's interaction with other threads.

- **Scheduling contexts** (SchedulingContexts; see Chapter 6) represent CPU time in seL4. Users can create scheduling contexts from untyped objects, however on creation scheduling contexts are *empty* and do not represent any time. Initially, there is a capability to SchedControl for each node, which allows scheduling context to be populated with parameters, which combined with priority control thread's access to CPU time.

**Endpoints** (see Chapter 4) facilitate message-passing communication between threads. IPC is synchronous: A thread trying to send or receive on an endpoint blocks until the message can be delivered. This means that message delivery only happens if a sender and a receiver rendezvous at the endpoint, and the kernel can deliver the message with a single copy (or without copying for short messages using only registers).

A capability to an endpoint can be restricted to be send-only or receive-only. Additionally, Endpoint capabilities can have the grant right, which allows sending capabilities as part of the message.

- **Reply objects** (see Chapter 4) track scheduling context donation and provide a container for single-use reply capabilities. They are provided by seL4\_Recv().

- **Notification Objects** (see Chapter 5) provide a simple signalling mechanism. A Notification is a word-size array of flags, each of which behaves like a binary semaphore. Operations are *signalling* a subset of flags in a single operation, polling to check any flags, and blocking until any are signalled. Notification capabilities can be signal-only or wait-only.

- Virtual Address Space Objects (see Chapter 7) are used to construct a virtual address space (or VSpace) for one or more threads. These objects largely directly correspond to those of the hardware, and as such are architecture-dependent. The kernel also includes ASID Pool and ASID Control objects for tracking the status of address spaces.

- **Interrupt Objects** (see Chapter 8) give applications the ability to receive and acknowledge interrupts from hardware devices. Initially, there is a capability to IRQControl, which allows for the creation of IRQHandler capabilities. An IRQHandler capability permits the management of a specific interrupt source associated with a specific device. It is delegated to a device driver to access an interrupt source. The IRQHandler object allows threads to wait for and acknowledge individual interrupts.

- **Untyped Memory** (see Section 2.4) is the foundation of memory allocation in the seL4 kernel. Untyped memory capabilities have a single method which allows the creation of new kernel objects. If the method succeeds, the calling thread gains access to capabilities to the newly-created objects. Additionally, untyped memory objects can be divided into a group of smaller untyped memory objects allowing delegation of part (or all) of the system's memory. We discuss memory management in general in the following sections.

### 2.4 Kernel Memory Allocation

The seL4 microkernel does not dynamically allocate memory for kernel objects. Instead, objects must be explicitly created from application-controlled memory regions via Untyped Memory capabilities. Applications must have explicit authority to memory (through these Untyped Memory capabilities) in order to create new objects, and all objects consume a fixed amount of memory once created. These mechanisms can be used to precisely control the specific amount of physical memory available to applications, including being able to enforce isolation of physical memory access between applications or a device. There are no arbitrary resource limits in the kernel apart from those dictated by the hardware<sup>1</sup>, and so many denial-of-service attacks via resource exhaustion are avoided.

At boot time, seL4 pre-allocates the memory required for the kernel itself, including the code, data, and stack sections (seL4 is a single kernel-stack operating system). It then creates an initial user thread (with an appropriate address and capability space). The kernel then hands all remaining memory to the initial thread in the form of capabilities to Untyped Memory, and some additional capabilities to kernel objects that were required to bootstrap the initial thread. These Untyped Memory regions can then be split into smaller regions or other kernel objects using the seL4\_Untyped\_Retype() method; the created objects are termed *children* of the original untyped memory object.

The user-level application that creates an object using seL4\_Untyped\_Retype() receives full authority over the resulting object. It can then delegate all or part of the authority it possesses over this object to one or more of its clients.

Untyped memory objects represent two different types of memory: general purpose memory, or device memory. *General purpose* memory can be untyped into any other object type and used for any operation on untyped memory provided by the kernel. *Device memory* covers memory regions reserved for devices as determined by the hardware platform, and usage of these objects is restricted by the kernel in the following ways:

- Device untyped objects can only be retyped into frames or other untyped objects; developers cannot, for example, create an endpoint from device memory.

- Frame objects retyped from device untyped objects cannot be set as thread IPC buffers, or used in the creation of an ASID pool

The type attribute (whether it represents *general purpose* or *device* memory) of a child untyped object is inherited from its parent untyped object. That is, any child of a device untyped will also be a device untyped. Developers cannot change the type attribute of an untyped.

#### 2.4.1 Reusing Memory

The model described thus far is sufficient for applications to allocate kernel objects, distribute authority among client applications, and obtain various kernel services provided by these objects. This alone is sufficient for a simple static system configuration.

The seL4 kernel also allows Untyped Memory regions to be reused. Reusing a region of memory is allowed only when there are no dangling references (i.e., capabilities) left to the objects inside that memory. The kernel tracks *capability derivations*, i.e., the children generated by the methods seL4\_Untyped\_Retype(), seL4\_CNode\_Mint(), seL4\_CNode\_Copy(), and seL4\_CNode\_Mutate().

<sup>&</sup>lt;sup>1</sup>The treatment of virtual ASIDs imposes a fixed number of address spaces. This limitation is to be removed in future versions of seL4.

The tree structure so generated is termed the *capability derivation tree* (CDT).<sup>2</sup> For example, when a user creates new kernel objects by retyping untyped memory, the newly created capabilities would be inserted into the CDT as children of the untyped memory capability.

For each Untyped Memory region, the kernel keeps a *watermark* recording how much of the region has previously been allocated. Whenever a user requests the kernel to create new objects in an untyped memory region, the kernel will carry out one of two actions: if there are already existing objects allocated in the region, the kernel will allocate the new objects at the current watermark level, and increase the watermark. If all objects previously allocated in the region have been deleted, the kernel will reset the watermark and start allocating new objects from the beginning of the region again.

Finally, the seL4\_CNode\_Revoke() method provided by CNode objects destroys all capabilities derived from the argument capability. Revoking the last capability to a kernel object triggers the *destroy* operation on the now unreferenced object. This simply cleans up any in-kernel dependencies between it, other objects and the kernel.

By calling seL4\_CNode\_Revoke() on the original capability to an untyped memory object, the user removes all of the untyped memory object's children—that is, all capabilities pointing to objects in the untyped memory region. Thus, after this invocation there are no valid references to any object within the untyped region, and the region may be safely retyped and reused.

#### 2.4.2 Summary of Object Sizes

When retyping untyped memory it is useful to know how much memory the object will require. Object sizes are defined in libsel4.

Note that CNodes and Untyped Objects have variables sizes. When retyping untyped memory into CNodes or breaking an Untyped Object into smaller Untyped Objects, the size\_bits argument to seL4\_Untyped\_Retype() is used to specify the size of the resulting objects. For all other object types, the size is fixed, and the size\_bits argument to seL4\_Untyped\_Retype() is ignored.

A single call to seL4\_Untyped\_Retype() can retype a single Untyped Object into multiple objects. The number of objects to create is specified by its num\_objects argument. All created objects must be of the same type, specified by the type argument. In the case of variable-sized objects, each object must also be of the same size. If the size of the memory area needed (calculated by the object size multiplied by num\_objects) is greater than the remaining unallocated memory of the Untyped Object, an error will result.

$<sup>^{2}</sup>$ Although the CDT conceptually is a separate data structure, it is implemented as part of the CNode object and so requires no additional kernel meta-data.

## Chapter 3

# **Capability Spaces**

Recall from Section 2.1 that seL4 implements a capability-based access control model. Each userspace thread has an associated *capability space* (CSpace) that contains the capabilities that the thread possesses, thereby governing which resources the thread can access.

Recall that capabilities reside within kernel-managed objects known as CNodes. A CNode is a table of slots, each of which may contain a capability. This may include capabilities to further CNodes, forming a directed graph. Conceptually a thread's CSpace is the portion of the directed graph that is reachable starting with the CNode capability that is its CSpace root.

A CSpace address refers to an individual slot (in some CNode in the CSpace), which may or may not contain a capability. Threads refer to capabilities in their CSpaces (e.g. when making system calls) using the address of the slot that holds the capability in question. An address in a CSpace is the concatenation of the indices of the CNode capabilities forming the path to the destination slot; we discuss this further in Section 3.3.

Recall that capabilities can be copied and moved within CSpaces, and also sent in messages (message sending will be described in detail in Section 4.2.2). Furthermore, new capabilities can be *minted* from old ones with a subset of their rights. Recall, from Section 2.4.1, that seL4 maintains a *capability derivation tree* (CDT) in which it tracks the relationship between these copied capabilities and the originals. The revoke method removes all capabilities (in all CSpaces) that were derived from a selected capability. This mechanism can be used by servers to restore sole authority to an object they have made available to clients, or by managers of untyped memory to destroy the objects in that memory so it can be retyped.

seL4 requires the programmer to manage all in-kernel data structures, including CSpaces, from userspace. This means that the userspace programmer is responsible for constructing CSpaces as well as addressing capabilities within them. This chapter first discusses capability and CSpace management, before discussing how capabilities are addressed within CSpaces, i.e. how applications can refer to individual capabilities within their CSpaces when invoking methods.

## 3.1 Capability and CSpace Management

#### 3.1.1 CSpace Creation

CSpaces are created by creating and manipulating CNode objects. When creating a CNode the user must specify the number of slots that it will have, and this determines the amount of memory that it will use. Each slot requires 16 bytes of physical memory and has the capacity to hold exactly one capability. Like any other object, a CNode must be created by calling seL4\_Untyped\_Retype() on an appropriate amount of untyped memory (see Section 2.4.2). The caller must therefore have a capability to enough untyped memory as well as enough free capability slots available in existing CNodes for the seL4\_Untyped\_Retype() invocation to succeed.

#### 3.1.2 CNode Methods

Capabilities are managed largely through invoking CNode methods.

CNodes support the following methods:

- seL4\_CNode\_Mint() creates a new capability in a specified CNode slot from an existing capability. The newly created capability may have fewer rights than the original and a different guard (see Section 3.3.1). seL4\_CNode\_Mint() can also create a badged capability (see Section 4.2.1) from an unbadged one.

- seL4\_CNode\_Copy() is similar to seL4\_CNode\_Mint(), but the newly created capability

has the same badge and guard as the original.

- seL4\_CNode\_Move() moves a capability between two specified capability slots. You

cannot move a capability to the slot in which it is currently.

- seL4\_CNode\_Mutate() can move a capability similarly to seL4\_CNode\_Move() and also reduce its rights similarly to seL4\_CNode\_Mint(), although without an original copy remaining.

- seL4\_CNode\_Rotate() moves two capabilities between three specified capability slots. It is essentially two seL4\_CNode\_Move() invocations: one from the second specified slot to the first, and one from the third to the second. The first and third specified slots may be the same, in which case the capability in it is swapped with the capability in the second slot. The method is atomic; either both or neither capabilities are moved.

- seL4\_CNode\_Delete() removes a capability from the specified slot.

- seL4\_CNode\_Revoke() is equivalent to calling seL4\_CNode\_Delete() on each derived child of the specified capability. It has no effect on the capability itself, except in very specific circumstances outlined in Section 3.2.

- seL4\_CNode\_CancelBadgedSends() cancels any outstanding sends that use the same badge and object as the specified capability.

#### 3.1.3 Capabilities to Newly-Retyped Objects

When retyping untyped memory into objects with seL4\_Untyped\_Retype(), capabilities to the newly-retyped objects are placed in consecutive slots in a CNode specified by its root, node\_index, and node\_depth arguments. The node\_offset argument specifies the index into the CNode at which the first capability will be placed. The num\_objects argument specifies the number of capabilities (and, hence, objects) to create. All slots must be empty or an error will result. All resulting capabilities will be placed in the same CNode.

#### 3.1.4 Capability Rights

As mentioned previously, some capability types have *access rights* associated with them. Currently, access rights are associated with capabilities for Endpoints (see Chapter 4), Notifications (see Chapter 5) and Pages (see Chapter 7). The access rights associated with a capability determine the methods that can be invoked. seL4 supports three orthogonal access rights, which are Read, Write and Grant. The meaning of each right is interpreted relative to the various object types, as detailed in Table 3.1.

When an object is first created, the initial capability that refers to it carries the maximum set of access rights. Other, less-powerful capabilities may be manufactured from this original capability, using methods such as seL4\_CNode\_Mint() and seL4\_-CNode\_Mutate(). If a greater set of rights than the source capability is specified for the destination capability in either of these invocations, the destination rights are silently downgraded to those of the source.

| Type         | Read                               | Write                              | Grant                                                                 |

|--------------|------------------------------------|------------------------------------|-----------------------------------------------------------------------|

| Endpoint     | Required to receive.               | Required to send.                  | Required to send ca-<br>pabilities (including<br>reply capabilities). |

| Notification | Required to wait.                  | Required to signal.                | N/A                                                                   |

| Page         | Required to map the page readable. | Required to map the page writable. | N/A                                                                   |

Table 3.1: seL4 access rights.

#### 3.1.5 Capability Derivation Tree

As mentioned in Section 2.4.1, seL4 keeps track of capability derivations in a capability derivation tree.

Various methods, such as seL4\_CNode\_Copy() or seL4\_CNode\_Mint(), may be used to create derived capabilities. Not all capabilities support derivation. In general, only *original* capabilities support derivation invocations, but there are exceptions. Table 3.2 summarises the conditions that must be met for capability derivation to succeed for the various capability types, and how capability-derivation failures are reported in each case. The capability types not listed can be derived once.

| Cap Type             | Conditions for Derivation    | Error Code on Derivation Failure |

|----------------------|------------------------------|----------------------------------|

| ReplyCap             | Cannot be derived            | Dependent on syscall             |

| IRQControl           | Cannot be derived            | Dependent on syscall             |

| Untyped              | Must not have children (Sec- | seL4_RevokeFirst                 |

|                      | tion $3.2$ )                 |                                  |

| Page Table           | Must be mapped               | ${\tt seL4\_Illegal0peration}$   |

| Page Directory       | Must be mapped               | ${\tt seL4\_Illegal0peration}$   |

| IO Page Table (IA-32 | Must be mapped               | ${\tt seL4\_Illegal0peration}$   |

| only)                |                              |                                  |

Table 3.2: Capability derivation.

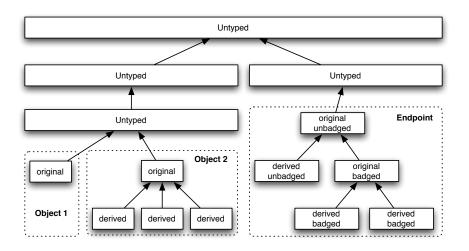

Figure 3.1: Example capability derivation tree.

Figure 3.1 shows an example capability derivation tree that illustrates a standard scenario: the top level is a large untyped capability, the second level splits this capability into two regions covered by their own untyped caps, both are children of the first level. The third level on the left is a copy of the level 2 untyped capability. Untyped capabilities when copied always create children, never siblings. In this scenario, the untyped capability was typed into two separate objects, creating two capabilities on level 4, both are the original capability to the respective object, both are children of the untyped capability they were created from.

Ordinary original capabilities can have one level of derived capabilities. Further copies of these derived capabilities will create siblings, in this case remaining on level 5. There is an exception to this scheme for Endpoint and Notification capabilities — they support an additional layer of depth though *badging*. The original Endpoint or *Notification* capability will be unbadged. Using the mint method, a copy of the capability with a specific *badge* can be created (see Section 4.2.1, Section 5.1). This new, badged capability to the same object is treated as an original capability (the "original badged endpoint capability") and supports one level of derived children like other capabilities.

## 3.2 Deletion and Revocation

Capabilities in seL4 can be deleted and revoked. Both methods primarily affect capabilities, but they can have side effects on objects in the system where the deletion or revocation results in the destruction of the last capability to an object.

As described above, seL4\_CNode\_Delete() will remove a capability from the specified CNode slot. Usually, this is all that happens. If, however, it was the last typed capability to an object, this object will now be destroyed by the kernel, cleaning up all remaining in-kernel references and preparing the memory for re-use.

If the object to be destroyed was a capability container, i.e. a TCB or CNode, the destruction process will delete each capability held in the container, prior to destroying the container. This may result in the destruction of further objects if the contained capabilities are the last capabilities.<sup>1</sup>

The seL4\_CNode\_Revoke() method will seL4\_CNode\_Delete() all CDT children of the specified capability, but will leave the capability itself intact. If any of the revoked child capabilities were the last capabilities to an object, the appropriate destroy operation is triggered.

Note: seL4\_CNode\_Revoke() may only partially complete in two specific circumstances. The first being where a CNode containing the last capability to the TCB of the thread performing the revoke (or the last capability to the TCB itself) is deleted as a result of the revoke. In this case the thread performing the revoke is destroyed during the revoke and the revoke does not complete. The second circumstance is where the storage containing the capability that is the target of the revoke is deleted as a result of the revoke. In this case, the authority to perform the revoke is removed during the operation and the operation stops part way through. Both these scenarios can be and should be avoided at user-level by construction.

Note that for page tables and page directories seL4\_CNode\_Revoke() will not revoke frame capabilities mapped into the address space. They will only be unmapped from the space.

### 3.3 CSpace Addressing

When performing a system call, a thread specifies to the kernel the capability to be invoked by giving an address in its CSpace. This address refers to the specific slot in

<sup>&</sup>lt;sup>1</sup>The recursion is limited as if the last capability to a CNode is found within the container, the found CNode is not destroyed. Instead, the found CNode is made unreachable by moving the capability pointing to the found CNode into the found cnode itself, by swapping the capability with the first capability in the found cnode, and then trying to delete the swapped capability instead. This breaks the recursion.

The result of this approach is that deleting the last cap to the root CNode of a CSpace does not recursively delete the entire CSpace. Instead, it deletes the root CNode, and the branches of the tree become unreachable, potentially including the deleting of some of the unreachable CNode's caps to make space for the self-referring capability. The practical consequence of this approach is that CSpace deletion requires user-level to delete the tree leaf first if unreachable CNodes are to be avoided. Alternatively, any resulting unreachable CNodes can be cleaned up via revoking a covering untyped capability, however this latter approach may be more complex to arrange by construction at user-level.

the caller's CSpace that contains the capability to be invoked.

CSpaces are designed to permit sparsity, and the process of looking-up a capability address must be efficient. Therefore, CSpaces are implemented as *guarded page tables*.

As explained earlier, a CSpace is a directed graph of CNode objects, and each CNode is a table of slots, where each slot can either be empty, or contain a capability, which may refer to another CNode. Recall from Section 2.3 that the number of slots in a CNode must be a power of two. A CNode is said to have a *radix*, which is the power to which two is raised in its size. That is, if a CNode has  $2^k$  slots, its radix would be k. The kernel stores a capability to the root CNode of each thread's CSpace in the thread's TCB. Conceptually, a CNode capability stores not only a reference to the CNode to which it refers, but also carries a *guard* value, explained in Section 3.3.1.

#### 3.3.1 Capability Address Lookup

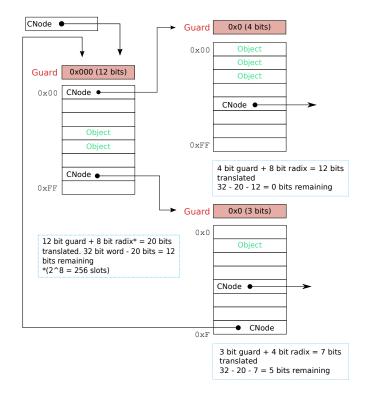

Like a virtual memory address, a capability address is simply an integer. Rather than referring to a location of physical memory (as does a virtual memory address), a capability address refers to a capability slot. When looking up a capability address presented by a userspace thread, the kernel first consults the CNode capability in the thread's TCB that defines the root of the thread's CSpace. It then compares that CNode's guard value against the most significant bits of the capability address. If the two values are different, lookup fails. Otherwise, the kernel then uses the next most-significant radix bits of the capability refers. The slot s identified by these next radix bits might contain another CNode capability or contain something else (including nothing). If s contains a CNode capability c and there are remaining bits (following the radix bits) in the capability address that have yet to be translated, the lookup process repeats, starting from the CNode capability c and using these remaining bits of the capability address in question refers to the capability slot s.

Figure 3.2 demonstrates a valid CSpace with the following features:

- a top level CNode object with a 12-bit guard set to 0x000 and 256 slots;

- a top level CNode with direct object references;

- a top level CNode with two second-level CNode references;

- second level CNodes with different guards and slot counts;

- a second level CNode that contains a reference to a top level CNode;

- a second level CNode that contains a reference to another CNode where there are some bits remaining to be translated;

- a second level CNode that contains a reference to another CNode where there are no bits remaining to be translated; and

- object references in the second level CNodes.

Figure 3.2: An example CSpace demonstrating object references at all levels, various guard and radix sizes and internal CNode references.

It should be noted that Figure 3.2 demonstrates only what is possible, not what is usually practical. Although the CSpace is legal, it would be reasonably difficult to work with due to the small number of slots and the circular references within it.

#### 3.3.2 Addressing Capabilities

A capability address is stored in a CPointer (abbreviated CPTR), which is an unsigned integer variable. Capabilities are addressed in accordance with the translation algorithm described above. Two special cases involve addressing CNode capabilities themselves and addressing a range of capability slots.

Recall that the translation algorithm described above will traverse CNode capabilities while there are address bits remaining to be translated. Therefore, in order to address a CNode capability, the user must supply not only a capability address but also specify the maximum number of bits of the capability address that are to be translated, called the *depth limit*.

Certain methods, such as seL4\_Untyped\_Retype(), require the user to provide a range of capability slots. This is done by providing a base capability address, which refers to the first slot in the range, together with a window size parameter, specifying the number of slots (with consecutive addresses, following the base slot) in the range.

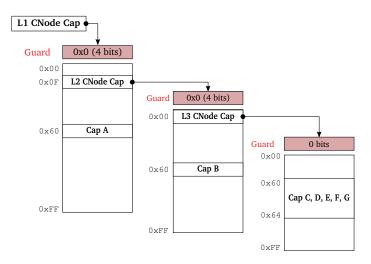

Figure 3.3 depicts an example CSpace. In order to illustrate these ideas, we determine the address of each of the 10 capabilities in this CSpace.

Figure 3.3: An arbitrary CSpace layout.

- Cap A. The first CNode has a 4-bit guard set to 0x0, and an 8-bit radix. Cap A resides in slot 0x60 so it may be referred to by any address of the form 0x060xxxxx (where xxxxx is any number, because the translation process terminates after translating the first 12 bits of the address). For simplicity, we usually adopt the address 0x06000000.

- **Cap B.** Again, the first CNode has a 4-bit guard set to 0x0, and an 8-bit radix. The second CNode is reached via the L2 CNode Cap. It also has a 4-bit guard of 0x0 and Cap B resides at index 0x60. Hence, Cap B's address is 0x00F06000. Translation of this address terminates after the first 24 bits.

- **Cap C.** This capability is addressed via both CNodes. The third CNode is reached via the L3 CNode Cap, which resides at index 0x00 of the second CNode. The third CNode has no guard and Cap C is at index 0x60. Hence, its address is 0x00F00060. Translation of this address leaves 0 bits untranslated.

- **Caps C–G.** This range of capability slots is addressed by providing a base address (which refers to the slot containing Cap C) of 0x00F00060 and a window size of 5.

- L2 CNode Cap. Recall that to address a CNode capability, the user must supply not only a capability address but also specify the depth limit, which is the maximum number of bits to be translated. L2 CNode Cap resides at offset 0x0F of the first CNode, which has a 4-bit guard of 0x0. Hence, its address is 0x00F00000, with a depth limit of 12 bits.

- L3 CNode Cap. This capability resides at index 0x00 of the second CNode, which is reached by the L2 CNode Cap. The second CNode has a 4-bit guard of 0x0. Hence, the capability's address is 0x00F00000 with a depth limit of 24 bits. Note that the addresses of the L2 and L3 CNode Caps are the same, but that their depth limits are different.

In summary, to refer to any capability (or slot) in a CSpace, the user must supply its address. When the capability might be a CNode, the user must also supply a depth

limit. To specify a range of capability slots, the user supplies a starting address and a window size.

## 3.4 Lookup Failure Description

When a capability lookup fails, a description of the failure is given to either the calling thread or the thread's exception handler in its IPC buffer. The format of the description is always the same but may occur at varying offsets in the IPC buffer depending on how the error occurred. The description format is explained below. The first word indicates the type of lookup failure and the meaning of later words depend on this.

#### 3.4.1 Invalid Root

A CSpace CPTR root (within which a capability was to be looked up) is invalid. For example, the capability is not a CNode cap.

| Data       | Meaning          |

|------------|------------------|

| Offset + 0 | seL4_InvalidRoot |

#### 3.4.2 Missing Capability

A capability required for an invocation is not present or does not have sufficient rights.

| Data                            | Meaning                |

|---------------------------------|------------------------|

| Offset + 0                      | seL4_MissingCapability |

| Offset + seL4_CapFault_BitsLeft | Bits left              |

#### 3.4.3 Depth Mismatch

When resolving a capability, a CNode was traversed that resolved more bits than was left to decode in the CPTR or a non-CNode capability was encountered while there were still bits remaining to be looked up.

| Data                             | Meaning                                |

|----------------------------------|----------------------------------------|

| Offset + 0                       | seL4_DepthMismatch                     |

| Offset + seL4_CapFault_BitsLeft  | Bits of CPTR remaining to decode       |

| Offset + seL4_CapFault_DepthMis- | Bits that the current CNode being tra- |

| match_BitsFound                  | versed resolved                        |

### 3.4.4 Guard Mismatch

When resolving a capability, a CNode was traversed with a guard size larger than the number of bits remaining or the CNode's guard did not match the next bits of the CPTR being resolved.

| Data                                                 | Meaning                          |

|------------------------------------------------------|----------------------------------|

| Offset + 0                                           | $seL4_GuardMismatch$             |

| Offset + seL4_CapFault_BitsLeft                      | Bits of CPTR remaining to decode |

| Offset + seL4_CapFault_GuardMis-<br>match_GuardFound | The CNode's guard                |

| Offset + seL4_CapFault_GuardMis-<br>match_BitsFound  | The CNode's guard size           |

## Chapter 4

# Message Passing (IPC)

The seL4 microkernel provides a message-passing IPC mechanism for communication between threads. The same mechanism is also used for communication with kernelprovided services. Messages are sent by invoking a capability to a kernel object. Messages sent to Endpoints are destined for other threads, while messages sent to other objects are processed by the kernel. This chapter describes the common message format, endpoints, and how they can be used for communication between applications.

## 4.1 Message Registers

Each message contains a number of message words and optionally a number of capabilities. The message words are sent to or received from a thread by placing them in its *message registers*. The message registers are numbered and the first few message registers are implemented using physical CPU registers, while the rest are backed by a fixed region of memory called the *IPC buffer*. The reason for this design is efficiency: very short messages need not use the memory. The IPC buffer is assigned to the calling thread (see Section 6.1 and Section 10.3.23).

Every IPC message also has a tag (structure seL4\_MessageInfo\_t). The tag consists of four fields: the label, message length, number of capabilities (the extraCaps field) and the capsUnwrapped field. The message length and number of capabilities determine either the number of message registers and capabilities that the sending thread wishes to transfer, or the number of message registers and capabilities that were actually transferred. The label is not interpreted by the kernel and is passed unmodified as the first data payload of the message. The label may, for example, be used to specify a requested operation. The capsUnwrapped field is used only on the receive side, to indicate the manner in which capabilities were received. It is described in Section 4.2.2.

The kernel assumes that the IPC buffer contains a structure of type seL4\_IPCBuffer as defined in Table 4.1. The kernel uses as many physical registers as possible to transfer IPC messages. When more arguments are transferred than physical message registers are available, the kernel begins using the IPC buffer's msg field to transfer arguments. However, it leaves room in this array for the physical message registers. For example, if an IPC transfer or kernel object invocation required 4 message registers (and there

| Туре                        | Name         | Description                                                      |

|-----------------------------|--------------|------------------------------------------------------------------|

| seL4_MessageInfo_t          | tag          | Message tag                                                      |

| seL4_Word[]                 | msg          | Message contents                                                 |

| seL4_Word                   | userData     | Base address of the structure, used by supporting user libraries |

| $seL4_CPtr[]$ (in)          | caps         | Capabilities to transfer                                         |

| <pre>seL4_CapData_t[]</pre> | badges       | Badges for endpoint capabilities re-                             |

| (out)                       |              | ceived                                                           |

| seL4_CPtr                   | receiveCNode | CPTR to a CNode from which to find<br>the receive slot           |

| seL4_CPtr                   | receiveIndex | CPTR to the receive slot relative to re-<br>ceiveCNode           |

| seL4_Word                   | receiveDepth | Number of bits of receiveIndex to use                            |

Table 4.1: Fields of the seL4\_IPCBuffer structure. Note that badges and caps use the same area of memory in the structure.

are only 2 physical message registers available on this architecture) then arguments 1 and 2 would be transferred via message registers and arguments 3 and 4 would be in msg[2] and msg[3]. This allows the user-level object-invocation stubs to copy the arguments passed in physical registers to the space left in the msg array if desired. The situation is similar for the tag field. There is space for this field in the seL4\_IPCBuffer structure, which the kernel ignores. User level stubs may wish to copy the message tag from its CPU register to this field, although the user level stubs provided with the kernel do not do this.

## 4.2 Endpoints

Endpoints allow a small amount of data and capabilities (namely the IPC buffer) to be transferred between two threads. Endpoint objects are invoked directly using the seL4 system calls described in Section 2.2.

IPC Endpoints uses a rendezvous model and as such is synchronous and blocking. An Endpoint object may queue threads either to send or to receive. If no receiver is ready, threads performing the seL4\_Send() or seL4\_Call() system calls will wait in a queue for the first available receiver. Likewise, if no sender is ready, threads performing the seL4\_Recv() system call or the second half of seL4\_ReplyRecv() will wait for the first available sender.

#### 4.2.1 Endpoint Badges

Endpoint capabilities may be *minted* to create a new endpoint capability with a *badge* attached to it, a data word chosen by the invoker of the *mint* operation. When a message is sent to an endpoint using a badged capability, the badge is transferred to the receiving thread's **badge** register.

An endpoint capability with a zero badge is said to be *unbadged*. Such a capability can be badged with the seL4\_CNode\_Mutate() or seL4\_CNode\_Mint() invocations on the CNode containing the capability. Endpoint capabilities with badges cannot be unbadged, rebadged or used to create child capabilities with different badges.

Only the low 28 bits of the badge are available for use. The kernel will silently ignore any usage of the high 4 bits.

#### 4.2.2 Capability Transfer

Messages may contain capabilities, which will be transferred to the receiver, provided that the endpoint capability invoked by the sending thread has Grant rights. An attempt to send capabilities using an endpoint capability without the Grant right will result in transfer of the raw message, without any capability transfer.

Capabilities to be sent in a message are specified in the sending thread's IPC buffer in the **caps** field. Each entry in that array is interpreted as a CPTR in the sending thread's capability space. The number of capabilities to send is specified in the **extraCaps** field of the message tag.

The receiver specifies the slot in which it is willing to receive a capability, with three fields within the IPC buffer: receiveCNode, receiveIndex and receiveDepth. These fields specify the root CNode, capability address and number of bits to resolve, respectively, to find the slot in which to put the capability. Capability addressing is described in Section 3.3.2.

A received capability has the same rights as the original, except if the *receiving* endpoint capability lacks the Write right. In this case, the rights on the sent capability are *diminished*, by stripping the Write right from the received copy of the capability.

Note that receiving threads may specify only one receive slot, whereas a sending thread may include multiple capabilities in the message. Messages containing more than one capability may be interpreted by kernel objects. They may also be sent to receiving threads in the case where some of the extra capabilities in the message can be *unwrapped*.